產品說明0

簡介

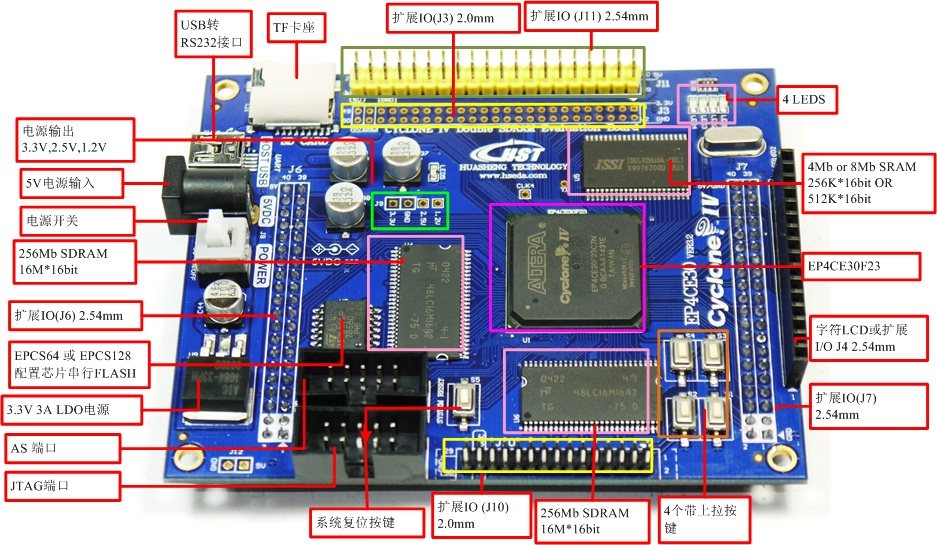

EP4CE30這款芯片採用經過優化的60-nm低功耗工藝,Cyclone IVE FPGA拓展了前一代Cyclone III FPGA的低功耗優勢。最新一代器件降低了內核電壓,與前一代產品相比,總功耗降低了25%。

核心板板採用是六層PCB設計,採用大容量管腳更多的BGA封裝,F484封裝,使整個核心板的性能和穩定性有了很大的提供,並同時為用戶提供大量的有效I/O(獨立I/O一共是157個。

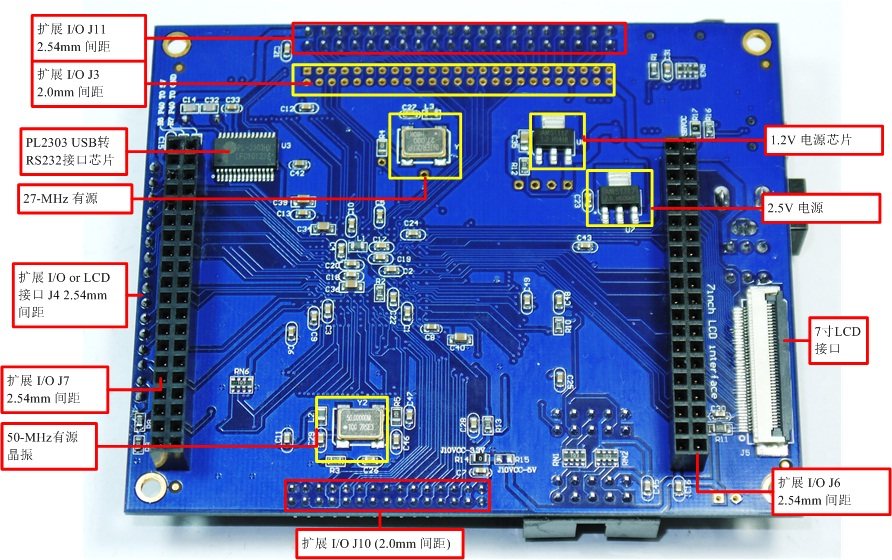

為了方便用戶進行程序調試和與PC通訊,我們增加了USB轉RS232接口,採用PL2303做USB轉串口設計。因為串口是很有用的一個功能。只是目前PC基本都已經取消了RS232接口。

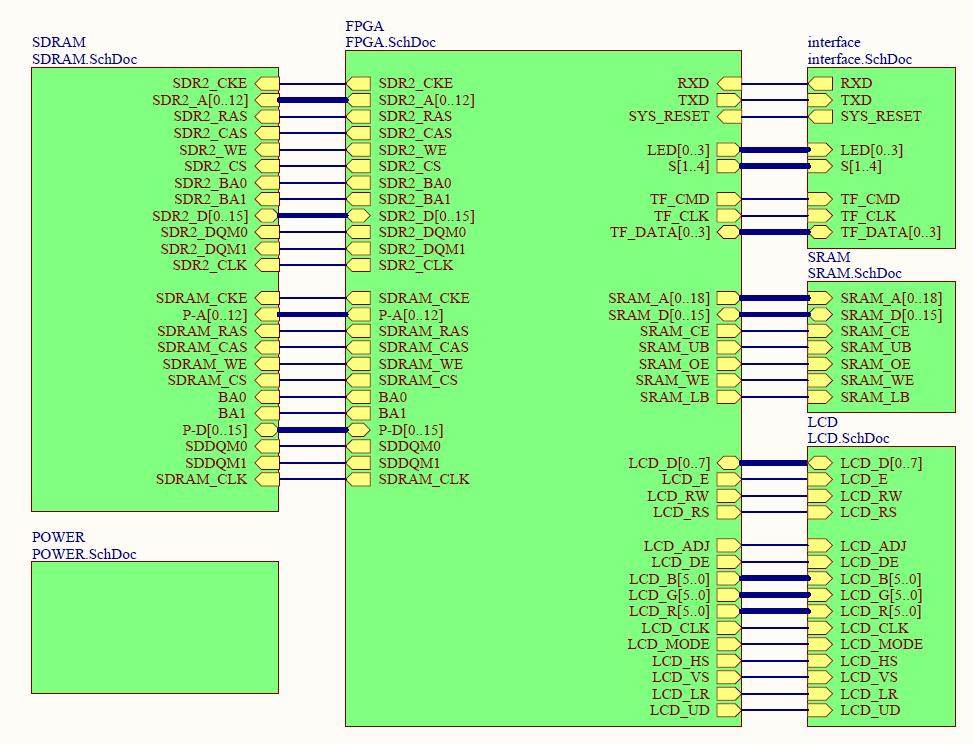

由於FPGA與存儲器直接進行高速數據交換。所以成在很多干擾因素,因此這也是很多開發板速度很難提高的關鍵原因。所以我們在設計的時候盡量靠近FPGA芯片。這樣就最大限度減少因為佈板所造成的干擾因素。 我們的開發板的2個獨立的的SDRAM和SRAM都採用獨立的數據地址總線進行控制。這樣就為使用者提供了更加方面靈活的設計途徑,2個獨立的SDRAM可以方便的做高速的數據處理的乒乓算法控制,或一個SDRAM做NIOS的程序存儲,另外一個做高速的DMA的數據存儲,最高速度可以到166M.

電源供電我們採用了LDO芯片和大容量濾波電容進行設計。因為板全速運行功耗很低(一般工作電流0.2-0.5A)。。所以採用超穩定性和低紋波的LDO供電。穩定性和低紋波干擾是開關電源沒有辦法比擬,可以做高性能的測量儀器級應用。我們可以穩定長時間提供3.3V, 3A工作電流。1.2V/1A, 2.5V/0.8A。

因為佈線合理,所以這塊開發板的NIOS能夠穩定高速運行在100M頻率以上。是您做系統評估或直接兼容最終應用產品最佳選擇。

用戶如果覺得自己做目標板麻煩。可以購買我們提供的多種擴展板。(本公司有各種視頻採集,輸出擴展板)或是通過J6,J7直接插到我們的EDA底板上(EDA4.1,EDA5.1,EDA6.1,EDA7.0四種不同可選擇主板)或是EDA試驗箱上。這樣就可以充分利用我們的EDA底板提供的功能多樣,完善外設資源。這樣就能輕易的構成一套售價低廉,功能強大的SOPC開發,評估系統。

系統結構圖

核心板頂層佈局圖

核心板底面佈局圖

原理圖頂層展示

系統資源

配套資料

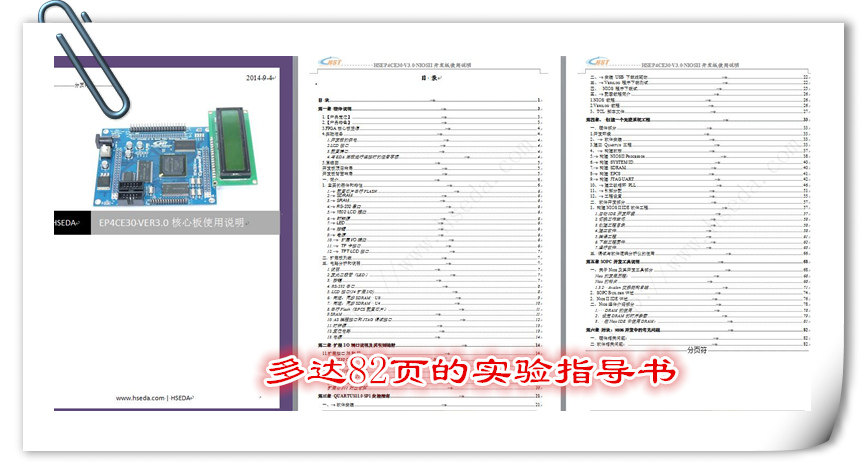

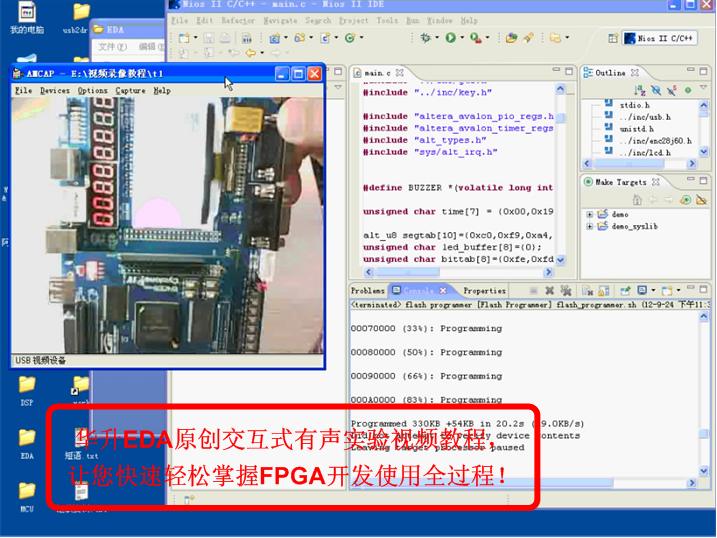

開發系統配套了1張DVD光盤,裡麵包含了原理圖,源代碼,原創教程, 以及大量視頻教程等等。

配套的FPGA開發軟件為:

Quartus II 11.0sp1

NIOS II IDE 11.0sp1

核心板實驗指導和使用說明目錄

大量教程教程讓您輕鬆上手

實驗代碼

單核心板板實驗代碼

EDA部分(verilog代碼):

- LCD1602顯示驅動

- SRAM讀寫測試

- 按鍵控制LED

- 流水燈實驗

- SD卡讀取圖片到SDRAM做緩衝然後輸出到VGA顯示圖片(要配合我們的24bit VGA音頻擴展模塊)

- SD卡讀取音頻文件然後輸出到音頻回放(要配合我們的24bit VGA音頻擴展模塊)

- 7寸LCD顯示驅動

SOPC (NIOS C代碼)

- 核心板系統全檢查SDRAM,SRAM讀寫測試,LCD1602顯示驅動

- SD卡讀取圖片到LCD7寸屏顯示(電子相冊)

- 基於QSYS創建一個LED點燈程序(包括完整視頻教程) quartus13.0

開發環境:(通過網盤給用戶)

- quartus11.0

- nios IDE 11.0

- MODESIM 10.0

- QUARUTUS 13.0

- NIOS IDE13.0